En primer lugar, para la implementación del reverberador seguiremos el esquema de generaración de la reverberación más simple pudiendo ser modificado y aumentado más adelante. Los esquemas más complejos de reverberación son montados encima de este esquema inicial, con lo cual si más adelante ampliamos la complejidad no tendremos problemas de diseño puesto que este será incremental. El esquema básico de reverberación:

La UC (Unidad de Control), se trata de una máquina de estados que será la que gobernará el circuito. Mediante la señal de "control" (no especificamos si la señal de control será de tipo bus ni su anchura hasta la implementación en circuito) y la señal "estados" que marcará en que estado se encuentra el dispositivo, conseguiremos la correcta sincronización de las órdenes en cada momento. La UC tendrá los siguientes estados :

1. Inicialización: se reseteará el circuito entero y se inicializará la memoria.

2. Funcionamiento: en el cual la señal de entrada sufrirá el algoritmo de revereberación y saldrá reverberada. El algoritmo de reverberación:

señal_salida(0) = señal_entrada(0),

señal_salida(t) = señal_entrada(t) + retardo, si t>0

siendo: retardo = señal_entrada(t-1)*A

El producto se efectuará desde la muestra primera hasta la penúltima con la atenuación A. Un pequeño ejemplo:

retardo(3) = A^3*señal(0)+A^2*señal(1)+A*señal(2) =>

señal_salida(3) = señal(3) + A*señal(2) + A^2*señal(1) + A^3*señal(0)

sea señal = señal_entrada

Definiremos más adelante el número de muestras de la señal anterior que guardamos en memoria. En principio guardaremos n>40 muestras, guardando la muestra 41 en la posición de la muestra 0.

3. Desconexión: La señal de entrada acaba y el circuito para de funcionar.

El AC97 es el circuito de recepción y emisión de la señal, posee ya integrados unos convertidos A/D para la entrada y D/A para la salida. La señal data_in es una señal que nos marcará la amplitud en ese instante y saldrá bit a bit debiendo ser guardada y enviada a modo de bus por el recibe señal.

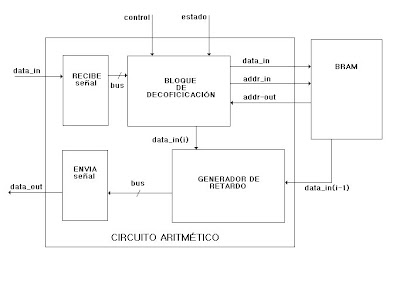

La gráfica más detallada del bloque aritmético: El bloque recibe señal y el bloque envía señal están intimamente relacionados con el AC97 y seu forma de enviar la señal, cogeremos 18 muestras de las que salgan del AC97 y las trataremos a modo de bus y en salida cogeremos el bus y lo enviaremos bit a bit.

El bloque recibe señal y el bloque envía señal están intimamente relacionados con el AC97 y seu forma de enviar la señal, cogeremos 18 muestras de las que salgan del AC97 y las trataremos a modo de bus y en salida cogeremos el bus y lo enviaremos bit a bit.

El Bloque de Decodificación se encarga de gobernar el algoritmo, marcando en que lugar deben ser guardadas las muestras dentro de la BRAM y en que orden deben salir las muestras para ir al generador de retardo.

El bloque generador de retardo crea el retardo de la señal y se la suma a la señal de entrada. En el debe estar especificado la atenuación. Deberemos calcular que factor de atenuación que usaremos en el circuito para que la señal no se atenúe ni demasiado rápido ni que no se aprecie este efecto.

La memoria BRAM almacenará las muestras de la señal en los instantes de tiempo.